## Prospective Article

# Device processing and junction formation needs for ultra-high power $Ga_2O_3$ electronics

Fan Ren, J.C. Yang, and Chaker Fares, Department of Chemical Engineering, University of Florida, Gainesville FL 32611, USA S.J. Pearton, Department of Materials Science and Engineering, University of Florida, Gainesville FL 32611, USA

Address all correspondence to S.J. Pearton at spear@mse.ufl.edu

(Received 16 November 2018; accepted 2 January 2019)

#### **Abstract**

A review is given of the future device processing needs for  $Ga_2O_3$  power electronics. The two main devices employed in power converters and wireless charging systems will be vertical rectifiers and metal oxide semiconductor field effect transistors (MOSFETs). The rectifiers involve thick epitaxial layers on conducting substrates and require stable Schottky contacts, edge termination methods to reduce electric field crowding, dry etch patterning in the case of trench structures, and low resistance Ohmic contacts in which ion implantation or low bandgap interfacial oxides are used to minimize the specific contact resistance. The MOSFETs also require spatially localized doping enhancement for low source/drain contact resistance, stable gate insulators with acceptable band offsets relative to the  $Ga_2O_3$  to ensure adequate carrier confinement, and enhancement mode capability. Attempts are being made to mitigate the absence of p-type doping capability for  $Ga_2O_3$  by developing p-type oxide heterojunctions with n-type  $Ga_2O_3$ . Success in this area would lead to minority carrier devices with better on-state performance and a much-improved range of functionality, such as p-i-n diodes, Insulated Gate Bipolar Transistors, and thyristors.

### Introduction

Wide-Bandgap (WBG) semiconductor devices are promising candidates for next-generation power electronic converters. [1-9] Power electronic applications range from on-chip power converters to very high voltage rectifiers for electric power transmission lines. [2,3,7-9] The potential application space includes power generation (solar and wind), power distribution and conversion in electricity grids, electric vehicles, server farms, and charging infrastructure. [2,7-9] High-voltage switching transistors used in these applications are required to have small ON resistance while providing very high blocking voltages in the OFF state. There are already kV-range power switches today, based on SiC and GaN. [7-9] These include a 1200 V direct-driven SiC Junction Field Effect Transistor power switch [8] and reliable GaN Metal Oxide–Semiconductor (MOS) Heterostructure Field Effect Transistors (HFETs). [9]

The  $\beta$ -polymorph of  $Ga_2O_3$  has an even larger power figure-of-merit than these two materials and is available in large area bulk and epitaxial layer form. The potential target for the  $Ga_2O_3$  devices, if the material quality continues to improve and appropriate device processing techniques are developed, will be in the 100s of kV–MV range. However, the prohibitive cost and limited variety of device types currently possible are still the main constraints before  $Ga_2O_3$  will be widely used in power electronics applications. One possible solution to mitigate these issues is hybrid switches: a combination of Si metal oxide semiconductor field effect transistors (MOSFETs) and WBG devices such as  $Ga_2O_3$  rectifiers or GaN

High Electron Mobility Transistors (HEMTs). In the latter case, 400 V/80A full bridge prototypes have been developed that show the ability to continuously turn off 400 V/80A@100 kHz and 400 V/40A@300 kHz with only one GaN device paralleled to two commercial Si MOSFETs. [2]  $Ga_2O_3$  would have an even larger voltage capability.

High-power ( $\sim$ 50 kW) is also required for fast wireless charging systems (WCS) in transportation applications. <sup>[2,6,7]</sup> In this application, the operating frequency of the WCS determines the size and configuration of the pad, the range of charging distance, and the quality factor of the resonant tank. Low power systems in the range  $3.7{-}11.0$  kW have been standardized to operate at 85 kHz. However, higher-power systems at  $10{-}22$  kHz reduce the switching loss in the inverter as well as conductive and magnetic losses in the power pad. At these frequencies, higher current is required to transfer the same power levels. Moreover, the mutual inductance is lower in case of dynamic wireless charging. SiC-based inverters are being developed for wireless vehicular charging applications and  $Ga_2O_3$  is a possible candidate due to the promising rectifier results reported to date. <sup>[2,3,6]</sup>

# Relevant properties and limitations of $Ga_2O_3$

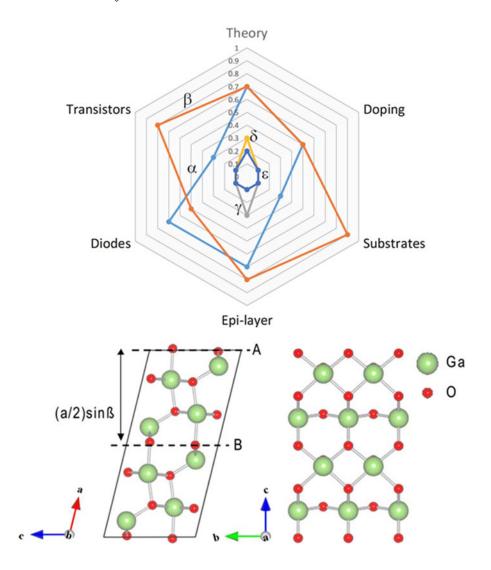

While there are a number of polymorphs of  $Ga_2O_3$ , the most stable and widely studied is monoclinic  $\beta$ - $Ga_2O_3$ . The corundum structure  $\alpha$ - $Ga_2O_3$  has a wider bandgap but is more difficult to stabilize. Figure 1 shows that the

Figure 1. (top) Qualitative representation of the technology development status of the different polymorphs of  $Ga_2O_3$  and (bottom left) unit cell along (010) direction and (bottom right) normal to the (100) surface of β- $Ga_2O_3$ .

$\beta$ -polymorph is the most developed in terms of devices, substrate, and epi layer availability. [2] Cross-sections of the  $\beta$ -polymorph crystal structure are shown at the bottom of the figure. For power switching applications, there are several drawbacks of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, including its low thermal conductivity and the absence of p-type doping capability. [1-4,6,10] The use of minority carrier assisted turn-on mechanisms are an intrinsic part of current power electronics. Ga<sub>2</sub>O<sub>3</sub>-based power devices would benefit from the availability of minority carrier so that PIN type diodes and IGBT (insulated gate bipolar transistor) type transistors can be fabricated. These devices preserve the high voltage blocking capacity while lowering the on-state resistance. Such devices exceed the theoretical limits of unipolar devices. As a consequence of its doping limitations, all Ga<sub>2</sub>O<sub>3</sub> devices are majority carrier type. [1-6] The two-terminal devices reported include rectifiers, UV solar-blind photoconductors, and photodetectors. [1-6,13-15] Three-terminal devices

reported include MESFETs and MOSFETs, mostly operating in depletion mode. At this stage, the theoretical critical field of  $\rm Ga_2O_3$  of~8 MV/c (extrapolated from other materials), has not been achieved experimentally, with values in the range 1.5–4.4 MV.cm $^{-1}$ .[15]

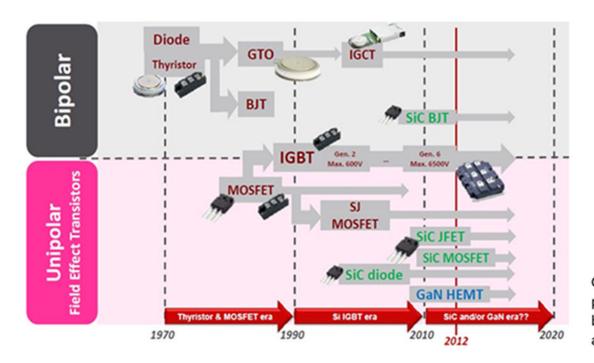

The absence of a p-type doping capability is due to the flatness of the valence band, which leads holes to effectively self-trap, giving rise to localize polarons. [10,14–19] There have been reports of p-type conductivity from ionized Ga vacancies at elevated temperature, [20] but extrinsic acceptors are not electrically active at room temperature. [21] Electronic devices are broadly classified as bipolar (minority carrier) or unipolar (majority carrier). Majority carrier devices usually switch faster and include Schottky diode rectifiers and MOSFETs. Minority carrier devices usually have better on-state performance and include p-i-n diode rectifiers, bipolar junction transistors (BJTs), IGBTs, and thyristors. [2,3] These latter two play a large role

in Si power electronics but will be challenging to achieve in  $Ga_2O_3$  because of the lack of p-type doping. The current approach is to employ p-type semiconductors such as SiC, NiO,  $Cu_2O$ , CuI, or diamond to make vertical p-n heterojunctions. [14–17] Figure 2 shows the evolution of Si power electronics and where SiC and GaN have begun to have an impact.

It is not clear that multiple junction devices in Ga<sub>2</sub>O<sub>3</sub> can be made successfully using these other p-type materials, since even single junction demonstrations have shown significant limitations. [15] The quality of the junctions must be very high in order to achieve acceptable performance in devices such as IGBTs and thyristors. These are three terminal devices with a controlling "gate" terminal but utilize different principles of operation. The thyristor has four alternating semiconductor layers (e.g., p-n-p-n), i.e., three p-n junctions and is basically a coupled pair of pnp and npn transistors. The outermost Pand N-type layers are the anode and cathode respectively, with the inner P-type layer acting as the "gate". It has three modes of operation, namely reverse blocking mode, forward blocking mode, and forward conducting mode. Once the gate is triggered, the thyristor is in forward conducting mode and keeps conducting until the forward current becomes less than the threshold holding current. Thyristors are mainly used in control of alternating currents. The IGBT has three terminals (emitter, collector, and gate). It can handle high powers at fast switching speed and has the combined features of both MOSFET and BJT. It is gate driven, like a MOSFET, and has current-voltage characteristics like BJTs. Therefore, it has the advantages of both high current handling capability and

ease of control. Si IGBT modules can handle kilowatts of power, with much larger capabilities for the wider gap materials if they have appropriate carrier lifetime and junction capability. Currently, the single p-n heterojunctions involving Ga<sub>2</sub>O<sub>3</sub> do not generally indicate minority carrier injection at low bias, indicating that a true p-n junction is not formed.

An important parameter in bipolar power devices is the minority carrier lifetime. Indirect semiconductors have a longer minority carrier lifetime compared to direct bandgap semiconductors. Lifetimes of 215 ps were reported for nonequilibrium holes created by e-beam excitation of n-type  $Ga_2O_3$ . [18]

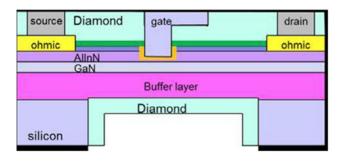

One limitation to Ga<sub>2</sub>O<sub>3</sub> material for power electronics is its low thermal conductivity at 11-27 W/mK, particularly when contrasted to the thermal conductivity of Si (130 W/mK), SiC (360–490 W/mK), and GaN (150–200 W/mK). [1-3] This means that thermal management approaches will be critical in power applications and these include top and bottom heat sinks and microfluidic channel to bring cooling fluid to the active region of the device. One approach for mitigating the low thermal conductivity of Ga<sub>2</sub>O<sub>3</sub> is by integrating diamond, AlN, or Cu as a high thermal conductivity heat spreader. [22–24] Integration of Ga<sub>2</sub>O<sub>3</sub> with diamond, which has nearly an order of magnitude higher thermal conductivity than Cu, is the most attractive option for high power Ga<sub>2</sub>O<sub>3</sub> devices. [22-24] However, diamond and Ga<sub>2</sub>O<sub>3</sub> are incompatible from a growth standpoint, as the growth atmosphere of one is detrimental to the other (H-plasma for Ga<sub>2</sub>O<sub>3</sub>, O-plasma for diamond). Development of approaches for the growth of Ga<sub>2</sub>O<sub>3</sub> on singlecrystal diamond, as well as CVD nanocrystalline diamond on

Can Ga<sub>2</sub>O<sub>3</sub> play a role beyond SiC and GaN?

Figure 2. Evolution of Si power electronics based on both majority and minority carrier devices and the beginning of the availability of SiC and GaN devices to provide higher performance.

both Ga<sub>2</sub>O<sub>3</sub> substrates and devices is an area of need. The existing embedded thermal management approaches developed for GaN, where cooling is built into the chip, substrate, and/or package to directly cool the heat generation sites using high-thermal-conductivity synthetic diamond material either to line microfluidic channels or to form the substrate of the RF chips, <sup>[2,6]</sup> is something that could be quickly applied to Ga<sub>2</sub>O<sub>3</sub>. Groups at the Naval Research Laboratories have demonstrated the integration of nanocrystalline diamond on both the front-side and backside of GaN HEMTs to effectively remove the heat from its source (drain edge of the gate) to heat sinks. <sup>[22–24]</sup> A schematic is shown in Fig. 3. These devices have achieved 20% (25–50 °C) reductions in device operating temperature while enhancing DC and RF performance. <sup>[22–24–4]</sup>

Given the basic properties of Ga<sub>2</sub>O<sub>3</sub>, where is it likely to have an impact? The status of p-n heterojunctions is too crude for practical applications. For rf applications, it is hard to see where Ga<sub>2</sub>O<sub>3</sub> brings advantages, although gate-allaround FinFETs can operate in accumulation mode in the on state. [25] Additionally, for lateral devices, the (Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> heterostructure has been recently demonstrated using modulation doping of the barrier layer, [26-30] as  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is nonpolar. There needs to be a major breakthrough, such as a >5 kV transistor or Ga<sub>2</sub>O<sub>3</sub> on diamond HFETs. The future of Ga<sub>2</sub>O<sub>3</sub> depends on its ability to find a profitable, sustainable commercial application. Solar-blind, ultra-violet photodetectors are a niche application (the 4.7-4.9 eV bandgap of Ga<sub>2</sub>O<sub>3</sub> renders it naturally solar-blind). The vertical Schottky barrier diodes matching the recovery characteristics of SiC SBDs have been demonstrated but offer no performance advantage at this time. [31,32] However, continued performance improvements would be a useful addition to the power electronics market as a fast, cheap, robust, low-loss switch.

### **Processing needs**

Vertical devices need field termination to avoid electric field crowding. For SiC and GaN, p-type termination regions such as guard rings and junction termination extensions, patterned selectively using either regrowth or implantation, have been

**Figure 3.** Schematic cross-section of GaN power transistor with integrated nanocrystalline diamond coatings for improved heat dissipation.

vital. Again, this is very difficult to implement in Ga<sub>2</sub>O<sub>3</sub> and simpler field termination must be employed.

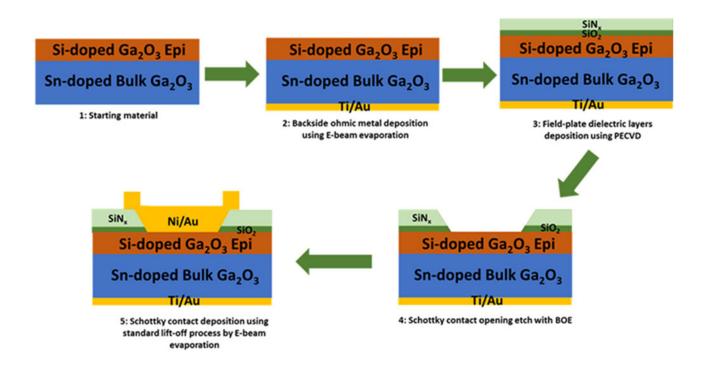

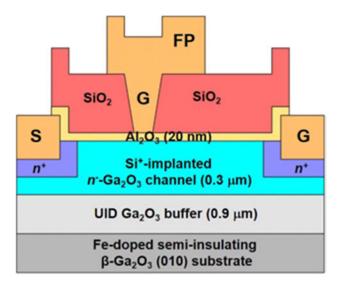

Let us examine the process sequence for a typical vertical geometry rectifier, shown in Fig. 4. This is relatively straightforward, involving a full area backside Ohmic contact, top Schottky contact, and overlap of this contact onto a dielectric layer. For a three terminal device, such as the MOSFET shown in Fig. 5, a simplified sequence involves the following steps:

- (i) Device Isolation—the active region is defined by mesa etching using low damage Cl<sub>2</sub>/BCl<sub>3</sub>-based inductively coupled plasma etching or by ion implantation to create highly resistive regions.

- (ii) Ohmic contact formation—a typical Ohmic on n-Ga $_2$ O $_3$  is a Ti/Pt/Au metal stack deposited by e-beam evaporated and annealed in O $_2$

- (iii) Gate recess etching—threshold voltage control by recess dry etching

- (iv) Gate oxide deposition—Al<sub>2</sub>O<sub>3</sub> or SiO<sub>2</sub> gate oxide deposited by ALD

- (v) Gate electrode metallization—typically Ni/Au metal stack e-beam evaporated for the gate formation

- (vi) O<sub>2</sub> ambient post-metallization annealing—post-metallization annealing in O<sub>2</sub> ambient to improve the interface quality of the Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> or SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub>.

Most of these same steps are generic to any two or three terminal  $Ga_2O_3$  device. In addition, while we show a  $Ga_2O_3$  channel MOSFET in Fig. 5, the use of  $(Al_xGa_{1-x})_2O_3$  two-dimensional electron gas (2DEG) channels allows high carrier density and mobility (high on-state driving current) and fast switching speed. [26–30]

All of the devices benefit from the addition of field plates to tailor the electric field profile, although multiple field plates have yet to be implemented and this might improve the dynamic on-resistance in FETs. Current collapse phenomena have been observed in MOSFETs but not studied to the extent they have in AlGaN/GaN HEMTs. This can be caused by reversible trapping into surface defects, AlGaO barrier bulk traps, interfacial traps at the AlGaO/GaO interface, and buffer traps. In recessed gate MOS configurations, there can be additional fixed/interface charges and plasma-induced recess damage. Again, the addition of field plates can reduce the current collapse and increase breakdown voltage by suppressed electric field reduce the probability of electron injection from the gate.

# **Contacts** *Ohmic contacts*

It is always challenging to make low resistance Ohmic contacts to wide bandgap semiconductors and generally some form of local doping enhancement by ion implantation,  $^{[12,33,34]}$  plasma exposure,  $^{[12]}$  or the addition of a low bandgap interlayer (AZO, ITO, InN)  $^{[35,36]}$  is used. Ion implantation is still relatively unexplored in  $Ga_2O_3$  in terms of choice of species, doses, and

Figure 4. Schematic of processing sequence for Ga<sub>2</sub>O<sub>3</sub> power rectifier, showing edge termination, thermally stable Schottky, and low resistance Ohmic.

annealing conditions. [12,34] It is necessary to achieve highly conductive surface layers for Ohmic contacts formation. In this case of ion implantation, this means carrier concentrations of  $10^{19}$ – $10^{20}$ /cm<sup>3</sup>. Activation annealing has typically been carried out at 900–1000 °C for 30 min, with activation percentages approaching 60%. [12,34] When annealed in N<sub>2</sub>, there was no change in surface morphology at temperatures below

Figure 5. Schematic of trench MOS Schottky diode. Reprinted with permission from ref. 5 (IEEE, 2018).

1150 °C, however, the addition of hydrogen to the annealing ambient lowered the temperature at which degradation was evident. [37,38] Thermodynamic analysis showed that the dominant reactions are  $Ga_2O_3(s)=Ga_2O(g)+O_2\ (g)$  in  $N_2$  and  $Ga_2O_3(s)+2H_2(g)=Ga_2O(g)+2H_2O\ (g)$  in a mixed flow of  $H_2$  and  $N_2.$  A simple expedient is to perform the implant activation anneals in  $O_2$  ambient. [37–40]

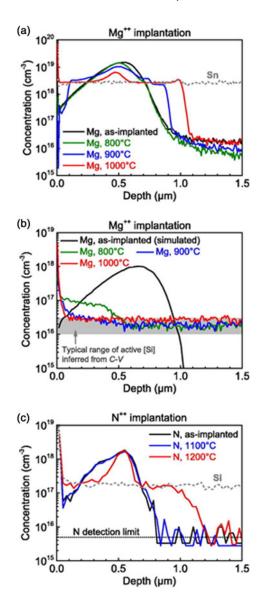

One surprising feature of the few implantation studies to date has been the high diffusivities of some of the implanted species. [34] Secondary Ion Mass Spectrometry (SIMS) depth profiles of Mg and N are shown in Fig. 6.[34] Significant Mg diffusion occurred at  $T_a \ge 900$  °C, with the as-implanted Gaussian Mg profile transformed into box-like with a sharp cutoff tail and a plateau concentration stabilized at the background donor (Sn) concentration. [34] This diffusion was independent of the impurity concentrations or the specific donor species involved. By contrast, implanted N profiles showed limited redistribution at 1200 °C and also stabilized at the background donor (Si) concentration of 2 ×  $10^{17}$ /cm<sup>3</sup>.

Sasaki et al. reported Ohmic contacts to  $Ga_2O_3$  using implanted Si to form  $n^+$  regions under the contact metal. [12] The implants were activated by 950 °C rapid-thermal annealing. Ohmic contacts made to these Si-implanted layers using Ti/Au metallization showed a specific contact resistivity of  $4.6\times10^{-6}/\Omega.\text{cm}^2$ , using a three-step contact process (BCl<sub>3</sub>/Ar etch, Ti/Au metal liftoff, 1 min. 450 °C RTA), Other variations employ additional metal layers such as Al, Ni, and Pt in the stack. It is not clear the insertion of these additional metal layers has had a positive impact on the Ohmic contact

**Figure 6.** SIMS profiles of Mg or N implants into  $Ga_2O_3$  before and after annealing at different temperatures. In (a), Mg profiles in heavily Sn-doped substrates before and annealing at 800–1000 °C, (b) Mg profiles in lightly Sn-doped substrates before and after annealing at 800–1000 °C and (c) N and Si profiles in undoped substrates before and after annealing at 1100–1200 °C. [Reprinted with permission from ref. 34 (American Institute of Physics, 2018)].

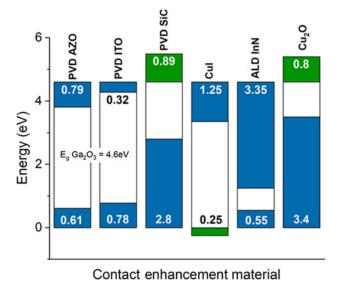

performance. [15] Carey et al. reported Al-doped ZnO (AZO) interlayers and compared to the Ohmic characteristics to Ti/Au. [36] For the AZO process, the Ga<sub>2</sub>O<sub>3</sub> was implanted with Si, followed by a 10/20/80 nm thick AZO/Ti/Au stack. The AZO contact exhibited nearly linear I-V characteristics even as-deposited. By comparison, the Ti/Au reference contact did not exhibit linear current-voltage characteristics even after annealing up to 600 °C. The contact resistance of 0.42  $\Omega$ ·mm (2.8 × 10<sup>-5</sup>  $\Omega$ /cm<sup>2</sup>) was reported for annealing at 400–600 °C, demonstrating the AZO/Ga<sub>2</sub>O<sub>3</sub> heterojunction

Figure 7. Band alignments for contact interlayer materials on Ga<sub>2</sub>O<sub>3</sub>.

has great potential for Ohmic contacts in  $Ga_2O_3$  devices. In a separate study,  $ITO/Ga_2O_3$  contacts were fabricated as well, with the lowest value for the specific contact resistance of  $0.60~\Omega$ -mm ( $6.3\times10^{-5}~\Omega$ /cm<sup>2</sup>) achieved after  $600~^{\circ}$ C annealing. Figure 7 shows the band alignments for some potential interfacial layers for reducing contact resistance on  $Ga_2O_3$ .

What is needed to further improve contact resistance? The versatility of ion implantation needs to be exploited. For most semiconductors, the implant activation temperature generally follows a two-thirds rule with respect to the melting point. [33] The melting temperature of  $Ga_2O_3$  is 1793–1820 °C, [1,39,40] so the 2/3 rule for implant activation annealing suggests temperatures in the range 1150-1250 °C. This is higher than generally employed to date. Annealing conditions consisting of a high temperature for a short duration are desirable for materials containing volatile elements, like oxides. These annealing conditions can give improved electrical properties and restrict surface degradation, dopant redistribution, and mobility degradation. The temperatures required for many wide bandgap semiconductors are beyond the capability of most rapid thermal annealing systems. Ga<sub>2</sub>O<sub>3</sub> decomposes into volatile lower oxides when heated under oxygen deficient atmospheres. The following decomposition reactions take place<sup>[36–40]</sup>:

$$\begin{split} Ga_2O_3(l,s) \, &\to \, 2GaO(g) + 1/2O_2(g), \, 2GaO(g) \\ &\to \, Ga_2O(g) + 1/2O_2(g), \, Ga_2O(g) \\ &\to \, 2Ga(g) + 1/2O_2(g). \end{split}$$

Thermal decomposition of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> becomes noticeable at temperatures above 1200 °C. Experiments on annealing at different temperatures and atmospheres showed stability of the (100) surface in O<sub>2</sub> to ~1300 °C, in N<sub>2</sub> or Ar to ~ 1200 °C,

and in the presence of  $H_2$  (5%  $H_2$  + 95% Ar) to ~600 °C for an annealing time of 10 h. [39,40] RTA conditions can extend these stability limits.

### Schottky contacts

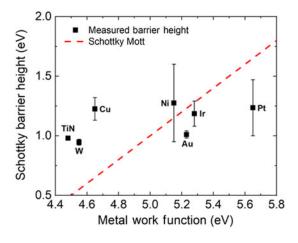

High barrier height, thermally stable (W, WNx, WCx) have yet to be explored for Ga<sub>2</sub>O<sub>3</sub>. Currently, high work function metals are typically used as Schottky contacts, with Ni and Pt the most common.<sup>[15,41–50]</sup> Prior to deposition, the surface is generally cleaned with organic solvents (acetone-methanol/isopropyl alcohol) usually with ultrasonic agitation and followed with various wet chemical treatments. Yao et al.[41] reported HCl+H<sub>2</sub>O<sub>2</sub> produced the highest Schottky barrier heights and lowest series resistances. The effect of the choice of metal on the Schottky behavior is still unclear. Scattered barrier heights with weak correlation to metal work function, as shown in Fig. 8, may indicate that there is at most only a partial Fermi level pinning due to defects and/or surface states, particularly on the (201) surface. Behavior closer to that predicted by the Schottky-Mott model is observed for (010) orientation. [51-54] Most of the reported Schottky barrier heights on β-Ga<sub>2</sub>O<sub>3</sub> are between ~1.0 and 1.5 eV. Electron-beam evaporation yields higher quality (near unity ideality factor) Schottky diodes in comparison to sputter-deposited contacts.<sup>[41]</sup>

### **Gate dielectrics for MOS gates**

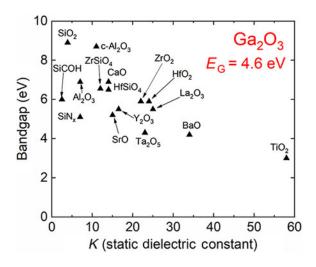

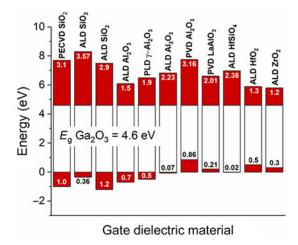

As shown in Fig. 9, there are a limited number of dielectrics with sufficient bandgaps to provide adequate conduction and valence band offsets on  $Ga_2O_3$ . There is definitely room to explore new options with bandgaps above 7 eV and with dielectric constants above 25. There are few choices with sufficiently high bandgap to get the desired >1 eV conduction and valence band offsets. Materials with a high dielectric constant (high-K) are desirable in  $Ga_2O_3$  FETs, since the higher

capacitance can reduce the effect of interface traps and therefore reduce the device operating voltage. Currently, the two most common dielectrics used are SiO2 and Al2O3. It has been found that the deposition method can have a very significant effect on the band alignment. [55-60] There are often variations in reported valence band offsets for dielectrics on semiconductors and some of the reasons documented include metal or carbon contamination, interfacial disorder, variations in dielectric composition, thermal conditions, strain, and surface termination effects. [59] Figure 10 shows there are differences of up to 1 eV in band alignments for SiO2 and Al2O3 on Ga<sub>2</sub>O<sub>3</sub> and (Al<sub>0.14</sub>Ga<sub>0.86</sub>)<sub>2</sub>O<sub>3</sub>, depending on whether they are deposited by sputtering or Atomic Layer Deposition. In the case of Al<sub>2</sub>O<sub>3</sub>, this changed the band alignment from nested (type I) to staggered gap (type II). The valence band offset at each heterointerface was measured using x-ray Photoelectron Spectroscopy and was determined to be -0.85 eV for sputtered  $Al_2O_3$  and 0.23 eV for ALD  $Al_2O_3$  on  $\beta$ - $(Al_{0.14}Ga_{0.86})_2O_3$ , while for SiO2 it was 0.6 eV for sputtered and 1.6 eV for ALD. These results are consistent with recent results showing that the surface of Ga<sub>2</sub>O<sub>3</sub> and related alloys are susceptible to severe changes during exposure to energetic ion environments.

More work needs to be done to understand the band offsets of p-type oxide heterojunctions (CuI, Ir<sub>2</sub>O<sub>3</sub>, SnO<sub>2</sub>) on Ga<sub>2</sub>O<sub>3</sub>. From Anderson's rule, <sup>[53]</sup> the conduction-band and the valence-band offsets are assumed to equal the differences of the electron affinities and the ionization energies, respectively, of the semiconductors forming the heterostructure and basically is the analog of the Schottky–Mott rule for metal–semiconductor or Schottky contacts. Monch<sup>[52]</sup> has proposed an alternative approach, in which the band-structure alignment at oxide heterostructures can be explained by interface-induced gap states directly related to the electronegativities of the semiconductors involved.

**Figure 8.** Barrier height metals on  $Ga_2O_3$  as a function of metal work function, showing only a weak correlation with the values expected from the Schottky–Mott relationship.

Figure 9. Dielectric constants and bandgaps for different dielectrics and potential contact materials on Ga<sub>2</sub>O<sub>3</sub>.

Figure 10. Band alignments for common dielectrics on Ga<sub>2</sub>O<sub>3</sub>.

# Field plates, impact ionization coefficients, and role of defects

To date, only a limited number of dielectrics have been used a gate overlap field plates and the optimization of material and geometry is largely unexplored. [61-65] To understand the breakdown characteristics of a power device, it is also important to know the impact ionization coefficients of electrons and holes as a function of the electric field in the semiconductor. [61] There are, as yet, no experimental measurements of these quantities for Ga<sub>2</sub>O<sub>3</sub>. The phenomenon of reverse breakdown is explained by avalanche multiplication, which involves impact ionization between host atoms and high-energy carriers. When a high-energy hole or electron under high electric field impacts an electron in the valence band, it will produce a new electron—hole pair (EHP). This newly generated EHP will cause other collisions and rapidly multiply carriers. Avalanche breakdown is defined to occur when. [66-70]

$$\int_{0}^{W_{D}} \alpha_{p} \exp \left[ \int_{0}^{x} (\alpha_{n} - \alpha_{p}) dx \right] dx > 1$$

$$\alpha_i = \alpha_0 \exp\left(\frac{-b_0}{E}\right)$$

where  $W_D$  is the depletion width,  $\alpha_a$  and  $\alpha_p$  are the ionization rates of electrons and holes. The electron ionization rate has been calculated for  $\text{Ga}_2\text{O}_3$  from a Boltzmann Transport Equation approach as  $\alpha_n = 0.79 \times 10^6$  exp  $(-2.92 \times 10^7)/E$  (cm<sup>-1</sup>). Using Chynoweth's equation  $(\alpha = a \ e^{-b/E})$ ,  $[^{68-70}]$  measurements for  $\text{Ga}_2\text{O}_3$  epitaxial layers grown on bulk  $\text{Ga}_2\text{O}_3$  substrates should produce values for  $\alpha$  and b for the impact ionization coefficient of electrons in  $\text{Ga}_2\text{O}_3$  at room temperature. Defects such as threading dislocations in the drift region of rectifiers lead to premature breakdown  $[^{71-78}]$  and it will be important to measure the changes in effective

impact ionization coefficients in material with known defect densities.

In the case of punch-through junction diode, the breakdown voltage is given by

$$BV_{PT} = E_c W_{PT} - \frac{q N_B W_{PT}^2}{2\varepsilon \varepsilon_0}$$

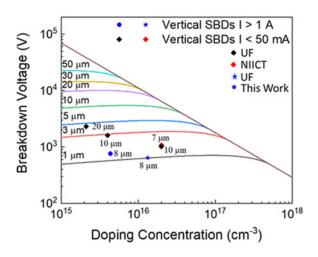

While the relevant relations are still being refined for  $Ga_2O_3$ , initial calculations of the same type can produce a plot of the theoretical breakdown voltage of  $Ga_2O_3$  punch-through diodes as a function of doping concentration and drift region thickness. Figure 11 is a plot of the theoretical breakdown voltage of  $Ga_2O_3$  punchthrough diodes as a function of doping concentration and drift region thickness, along with experimental values generated by us and others. A 3  $\mu$ m epi layer with doping concentration of  $10^{16}/cm^3$  theoretically has  $\sim 1800$  V breakdown voltage. The actual experimental value of breakdown voltage is far from these theoretical predictions and continued improvements in both materials and processing are needed to reduce this gap. [62-64]

# Trench etching (plasma), digital wet etch for damage cleanup

The dry etching studies to date on  $Ga_2O_3$  indicate that the etching mechanism is ion-driven, so there will be residual damage due to the ion bombardment. Optimization of the plasma conditions can minimize the amount of damage, but post-processing annealing or wet etch clean-up must be employed. In addition,  $\beta$ - $Ga_2O_3$  wafers are usually chemically mechanically polished and care must be taken to avoid residual damage layers. For subsequent growth or processing on these surfaces, etching and annealing to remove the damaged layer and create a step structure on the wafer surface are needed. Ohira and Arai<sup>[79]</sup> examined different etching reagents and temperatures

Figure 11. Breakdown voltage versus drift layer thickness for vertical  $\rm Ga_2O_3$  rectifiers, with experimentally reported values.

for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Only 47% HF at RT and 60.5% HNO<sub>3</sub> at 120 °C were found produce etching.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is resistant to other acid and basic solutions at room temperature. With the use of HF, the dissolution of Ga from Ga<sub>2</sub>O<sub>3</sub> linearly increased with etching time and with HF concentration. The etching rate of the (100) plane was found to be almost twice higher as compared to the (001) plane.

Photoelectrochemical etching has yet to be explored for Ga<sub>2</sub>O<sub>3</sub>. The dissolution rate of semiconductors may be altered in acid or base solutions by illumination with above bandgap light. The mechanism for photo-enhanced etching involves the creation of e-h pairs, the subsequent oxidative dissociation of the semiconductor into its component elements (a reaction that consumes the photo-generated holes) and the reduction of the oxidizing agent in the solution by reaction with the photo-generated electrons. Generally, n-type material is readily etched under these conditions, while p-type material is not due to the requirements for confining photo-generated holes at the semiconductor-electrolyte interface (i.e., the p-surface is depleted of holes because of the band-bending).

# Plasma processing and annealing can affect background n-type conductivity

Plasma exposure generally increases the n-type conductivity of the near-surface, while annealing in O2 ambients tends to decrease this conductivity.<sup>[15]</sup> There are at least two sources for electrical conductivity in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, namely residual impurities, such as the common hydrogenic donor impurities (ionization energy~30 meV) Si, Sn, Ge located on Ga sites, which provide the electron concentration at the level of about 10<sup>17</sup>/cm<sup>3</sup>, as well as hydrogen. The n-type conductivity can be reduced by adding the acceptors Mg, Be, and by annealing in O2. There are always native defects present prior to processing, such as the deep acceptors due to native defects  $V_{Ga}$ , at tetrahedral (Ga1) and octahedral (Ga2) sites. Their concentration increases with the partial pressure of oxygen during growth or annealing and leads to compensation of the n-type conductivity. There are also oxygen vacancies Vo at threefold coordinated sites (O1 and O2) and fourfold coordinated sites (O3). Theory indicates that all of these oxygen vacancy configurations are deep donors and have minimal effect on the conductivity. Shallow donors may include isolated Hi, as well as  $V_{\rm Ga}$ -H complexes that reduce the compensation effect of Ga vacancies. Hydrogen can occupy either interstitial (Hi) or substitutional sites (H<sub>O</sub>) and in both configurations can act as shallow donors. The theory also suggests that F and Cl on the O site are shallow donors and can contribute to conductivity. Fe-doping is used to create resistive material for buffers on FETs. Hall measurements of Fe doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> indicate the material remains weakly n-type even with the Fe doping, with an acceptor energy of 860 meV relative to the conduction band for the Fe deep acceptor.

Currently, the range of carrier concentrations available in bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> are  $10^{16}$ - $10^{19}$ /cm<sup>3</sup>, while in epitaxial layers it is from  $10^{16}$  to  $10^{20}$ /cm<sup>3</sup>, with maximum electron mobilities

of 150–170 in bulk samples and 120–130/cm<sup>2</sup>/V/sec in epitaxial layers.

#### **Conclusions**

Although high breakdown voltage devices can be fabricated using only majority carrier semiconductors, [80] low onresistance is difficult to achieve without minority carriers. The absence of  $p\text{-}Ga_2O_3$  is a major limitation. The low thermal conductivity is another major limitation. Process developments in Ohmic and rectifying contacts, gate dielectrics, and ion implantation continue to help improve device performance.

A challenge to the commercial viability of Ga<sub>2</sub>O<sub>3</sub> is the lack of a diverse supply chain for wafers and epi films. [81] Only one company provides Ga<sub>2</sub>O<sub>3</sub> substrates commercially, Tamura Corporation. Its spinoff, Novel Crystal Technology has commercialized Ga<sub>2</sub>O<sub>3</sub> epilayers by molecular beam epitaxy and halide vapor phase epitaxy. The one commercial (albeit limited availability) Ga<sub>2</sub>O<sub>3</sub> device is a rectifier fabricated using α-Ga<sub>2</sub>O<sub>3</sub> grown by mist-CVD by Flosfia, Inc. Northrop Grumman Synoptics has demonstrated Czochralski grown 2-inch boules of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, but these are not commercially available. [81] Agnitron has commercialized an MOCVD system. [81] Kyma Technologies and Structured Materials Industries have demonstrated a high-quality material. It will take a continued investment to allow maturity of Ga<sub>2</sub>O<sub>3</sub> device technology. Ga<sub>2</sub>O<sub>3</sub> will not displace SiC and GaN devices but possibly supplement them at high voltages.

### **Acknowledgments**

The work at UF is partially supported by Department of the Defense, Defense Threat Reduction Agency, HDTRA1-17-1-0011 (Jacob Calkins, monitor).

#### References

- Z. Galazka: β-Ga<sub>2</sub>O<sub>3</sub> for wide-bandgap electronics and optoelectronics. Semicond. Sci. Technol. 33, 113001 (2018). https://doi.org/10.1088/ 1361-6641/aadf78.

- B. Bayraktaroglu: Assesment of Gallium Oxide Technology, Air Force Research Lab, Devices for Sensing Branch, Aerospace Components and Subsystems Division, Report AFRL-RY-WP-TR-2017-0167 (2017).

- M. Higashiwaki and G.H. Jessen: Guest editorial: the dawn of gallium oxide microelectronics. Appl. Phys. Lett. 112, 060401 (2018).

- M.J. Tadjer, N.A. Mahadik, V. Wheeler, E.R. Glaser, L. Ruppalt, and A. D. Koehler: Editors' choice communication-A (001) β-Ga<sub>2</sub>O<sub>3</sub> MOSFET with +2.9 V threshold voltage and HfO<sub>2</sub> gate dielectric. ECS J. Solid State Sci. Technol. 5, P468–P470 (2016).

- M.H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki: Field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs with a breakdown voltage of over 750 V. IEEE Electron Device Lett. 37, 212–215 (2016).

- S.J. Pearton, J.C. Yang, P.H. Carey, F Ren, J. Kim, M.J. Tadjer, and M. A. Mastro: A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices. *Appl. Phys. Rev.* 5, 011301 (2018).

- X. Cheng: Overview of recent progress of semiconductor power devices based on wide bandgap materials. *IOP Conf. Ser.: Mater. Sci. Eng.* 439, 022033 (2018). https://doi.org/10.1088/1757-899X/439/2/022033.

- R. Singh and S. Sundaresan: 1200 V SiC Schottky rectifiers optimized for ≥250 °C operation with low junction capacitance Applied Power Electronics Conference and Exposition, pp. 226–228 (2013).

- Y. Eum, K. Oyama, and N. Otake: Highly reliable GaN MOS-HFET with high short-circuit capability International Symposium on Power Semiconductor Devices and Ic's, pp. 195–198 (2017).

- J.B. Varley, A. Janotti, C. Franchini, and C.G. Van de Walle: Role of self-trapping in luminescence and p-type conductivity of wide-band-gap oxides. *Phys. Rev. B* 85, 081109(R) (2012).

- A.T. Neal, S. Mou, S. Rafique, H. Zhao, E. Ahmadi, J.S. Speck, K. T. Stevens, J.D. Blevins, D.B. Thomson, N. Moser, K.D. Chabak, and G. H. Jessen: Donors and deep acceptors in β-Ga<sub>2</sub>O<sub>3</sub>. Appl. Phys. Lett. 113, 062101 (2018); https://doi.org/10.1063/1.5034474.

- K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi: Si-ion implantation doping in beta-Ga<sub>2</sub>O<sub>3</sub> and its application to fabrication of low-resistance ohmic contacts. *Appl. Phys. Express* 6, 086502 (2013).

- 13. M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi: Gallium oxide  $(Ga_2O_3)$  metal-semiconductor field-effect transistors on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates. *Appl. Phys. Lett.* **100**, 013504 (2012).

- T. Watahiki, Y. Yuda, A. Furukawa, M. Yamamuka, Y. Takiguchi, and S. Miyajima: Heterojunction p-Cu<sub>2</sub>O/n-Ga<sub>2</sub>O<sub>3</sub> diode with high breakdown voltage. Appl. Phys. Lett. 111, 222104 (2017).

- 15. M.A. Tadjer, N.A. Mahadik, J.A. Freitas, E.A. Glaser, A.D. Koehler, L. E. Luna, B.N. Feigelson, K.D. Hobart, F.J. Kub, and A. Kuramata: Ga<sub>2</sub>O<sub>3</sub> Schottky barrier and heterojunction diodes for power electronics applications, Proc. SPIE 10532, Gallium Nitride Materials and Devices XIII, 1053212 (23 February 2018); doi: 10.1117/12.2292211.

- Y. Kokubun, S. Kubo, and S. Nakagomi: All-oxide p-n heterojunction diodes comprising p-type NiO and n-type β- Ga<sub>2</sub>O<sub>3</sub>. Appl. Phys. Expr. 9, 091101 (2016).

- Nakagomi, K. Hiratsuka, Y. Kakuda, and Y. Kokubun: Beta-gallium oxide/SiC heterojunction diodes with high rectification ratios. *ECS J. Solid State Sci. Technol.* 6, Q3030–Q3034 (2017).

- 18. J. Lee, E. Flitsiyan, L. Chernyak, J. Yang, F. Ren, S.J. Pearton, B. Meyler, and Y.J. Salzman: Effect of 1.5 MeV electron irradiation on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> carrier lifetime and diffusion length. *Appl. Phys. Lett.* **112**, 082104 (2018); https://doi.org/10.1063/1.5011971.

- M. Higashiwaki, K. Sasaki, M.H. Wong, T. Kamimura, D. Krishnamurthy, A. Kuramata, T. Masui, and S. Yamakoshi: Depletion-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs on β-Ga<sub>2</sub>O<sub>3</sub> (010) substrates with Si-ion-implanted channel and contacts, *Electron Devices Meeting (IEDM)*, 2013 IEEE International, pages 28–32. IEEE, 2013.

- Chikoidze, A. Fellous, A. Perez-Tomas, G. Sauthier, T. Tchelidze, C. Ton-That, T. Huynh, M. Phillips, S. Russell, M. Jennings, B. Berini, F. Jomard, and Y. Dumont: P-type β-gallium oxide: a new perspective for power and optoelectronic devices. *Mater. Today Physics* 3, 118–126 (2017). https://doi.org/10.1016/j.mtphys.2017.10.002.

- A. Kyrtsos, M. Matsubara, and E. Bellotti: On the feasibility of p-type Ga<sub>2</sub>O<sub>3</sub>. Appl. Phys. Lett. **112**, 032108 (2018); https://doi.org/10.1063/1. 5009423

- M.A. Tadjer, T. Anderson, K.D. Hobart, T.I. Feygelson, J.D. Caldwell, C. R. Eddy, F.J. Kub, J.E. Butler, B. Pate, and J. Melngailis: Reduced self-heating in AlGaN/GaN HEMTs using nanocrystalline diamond heat-spreading films. *IEEE Electron Dev. Lett.* 33, 23–25 (2012).

- T.J. Anderson, A.D. Koehler, K.D. Hobart, M.J. Tadjer, T.I. Feygelson, J. K. Hite, B. Pate, F.J. Kub, and C.R. Eddy: Nanocrystalline diamond-gated AlGaN/GaN HEMT. *IEEE Electron Dev. Lett.* 34, 1382–1384 (2013).

- 24. D. Meyer, T. Feygelson, T. Anderson, J. Roussos, M. Tadjer, B. Downey, D. Katzer, B. Pate, M. Ancona, A. Koehler, K.D. Hobart, and C. Eddy: Large-signal RF performance of nanocrystalline diamond coated AlGaN/GaN high electron mobility transistors. *IEEE Electron Dev. Lett.* 35, 1013–1015 (2014).

- K. Chabak, N. Moser, A.J. Green, D.E. Walker, S.E. Tetlak, E. Heller, A. Crespo, R. Fitch, J. McCandless, K. Leedy, M. Baldini, G. Wagner, Z. Galazka, X. Li, and G. Jessen: Enhancement-mode Ga<sub>2</sub>O<sub>3</sub> wrap-gate fin field-effect transistors on native (100) β-Ga<sub>2</sub>O<sub>3</sub> substrate with high breakdown voltage. *Appl. Phys. Lett.* 109, 213501 (2016). https://doi. org/10.1063/1.4967931.

- 26. E. Ahmadi, O.S. Koksaldi, X. Zheng, T. Mates, Y. Oshima, U. Mishra, and J. Speck: Demonstration of  $\beta$ -(Al $_{\rm X}$  Ga $_{1-{\rm X}}$ ) $_2$ O $_3$ / $\beta$ -Ga $_2$ O $_3$  modulation doped field-effect transistors with Ge as dopant grown via plasma-assisted

- molecular beam epitaxy. *Appl. Phys. Expr.* **10**, 071101 (2017). https://doi.org/10.7567/APEX.10.071101.

- S. Krishnamoorthy, Z. Xia, C. Joishi, Y. Zhang, J. McGlone, J. Johnson, M. Brenner, A.R. Arehart, J. Hwang, S. Lodha, and S. Rajan: Modulation-doped β-(Al<sub>0.2</sub>Ga<sub>0.8</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> field-effect transistor. *Appl. Phys. Lett.* 111, 023502 (2017).

- Y. Zhang, C. Joishi, X. Xia, M. Brenner, S. Lodha, and S. Rajan: Demonstration of β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> double heterostructure field effect transistors. *Appl. Phys. Lett.* 112, 233503 (2018). https://doi.org/ 10.1063/1.5037095.

- Y. Zhang, A. Neal, S. Xia, C. Joishi, J.M. Johnson, Y. Zheng, S. Bajaj, M. Brenner, D. Dorsey, K. Chabak, G. Jessen, J. Hwang, S. Mou, J. P. Heremans, and RajanS: Demonstration of high mobility and quantum transport in modulation-doped β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> heterostructures. Appl. Phys. Lett. 112, 173502 (2018).

- R. Wakabayashi, M. Hattori, K. Yoshimatsu, K. Horiba, H Kumigashira, and A. Ohtomo: Band alignment at β-(AlxGa1-x)203/β-Ga203 (100) interface fabricated by pulsed-laser deposition. *Appl. Phys. Lett.* 112, 232103 (2018).

- 31. Å. Takatsuka, K. Sasaki, D. Wakimoto, Q. Thieu, R. Koishikawa, J. Arima, J. Hirabayashi, D. Inokuchi, Y. Fukumitsu, A. Kuramata, and S. Yamakoshi: Fast Recovery Performance of β-Ga<sub>2</sub>O<sub>3</sub> Trench MOS Schottky Barrier Diodes, 76<sup>th</sup> Dev. Res. Conf. Proc., 2018. DOI: 10.1109/DRC.2018.8442267.

- 32. J.C. Yang, F. Ren, Y.T. Chen, Y.T. Liao, C.W. Chang, J. Lin, M. Tadjer, S. J. Pearton, and A. Kuramata: Dynamic switching characteristics of 1 a forward current  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> rectifiers. *IEEE J. Electron Devices Society* (2019). DOI: 10.1109/JEDS.2018.2877495.

- J.C. Zolper: Ion implantation in group III-nitride semiconductors: a tool for doping and defect studies. J. Crystal Growth 178, 157–167 (1997). https://doi.org/10.1016/S0022-0248(97)00076-6.

- 34. M.H. Wong, C.H. Lin, A. Kuramata, S. Yamakoshi, H. Murakami, Y. Masataka, and M. Higashiwaki: Acceptor doping of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by Mg and N ion implantations. *Appl. Phys. Lett.* **113**, 102103 (2018). https://doi.org/10.1063/1.5050040.

- 35. P. Carey, J. Yang, F. Ren, D.C. Hays, S.J. Pearton, S. Jang, A. Kuramata, and I.I. Kravchenko: Improvement of ohmic contacts on Ga<sub>2</sub>O<sub>3</sub> through use of ITO-interlayers. *J. Vac. Sci. Technol. B.* 35, 061201 (2017).

- 36. P. Carey, J.C. Yang, F. Ren, D.C. Hays, S.J. Pearton, S. Jang, A. Kuramata, and I. Kravchenko: Ohmic contacts on N-type Ga<sub>2</sub>O<sub>3</sub> using AZO/Ti/Au. AIP. Adv. 7, 095313 (2017).

- 37. K. Hoshikawa, E. Ohba, T. Kobayashi, J. Yanagisawa, C. Miyagawa, and Y. Nakamura: Growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystals using vertical Bridgman method in ambient air. *J. Cryst. Growth* **447**, 36–41 (2016).

- R. Togashi, K. Nomura, C. Eguchi, T. Fukizawa, K. Goto, Q.T. Thieu, H. Murakami, Y. Kumagai, A. Kuramata, and S. Yamakoshi: Thermal stability of β-Ga<sub>2</sub>O<sub>3</sub> in mixed flows of H<sub>2</sub> and N<sub>2</sub>. *Japan. J. Appl. Phys.* 54, 041102 (2015). http://dx.doi.org/10.7567/JJAP.54.041102.

- W. Mu, Z. Jia, Y. Yin, Q. Hu, Y. Li, B. Wu, J. Zhang, and X. Tao: High quality crystal growth and anisotropic physical characterization of β-Ga<sub>2</sub>O<sub>3</sub> single crystals grown by EFG method. *J. Alloys Compounds* 714, 453 (2017)

- V.I. Nikolaev, V. Maslov, S. Stepanov, A. Pechnikov, V. Krymov, I. Nikitina, L. Guzilova, V. Bougrov, and A. Romanov: Growth and characterization of β-Ga<sub>2</sub>O<sub>3</sub> crystals. J. Cryst. Growth 457, 132–136 (2017).

- 41. Y. Yao, R.F. Davis, and L.M. Porter: Investigation of different metals as ohmic contacts to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>: comparison and analysis of electrical behavior, morphology and other physical properties. *J. Electron. Mater.* **46**, 2053 (2017).

- 42. Y. Yao, R. Gangireddy, J. Kim, K.K. Das, R.F. Davis, and L.M. Porter: Electrical behavior of  $\beta$ -Ga $_2$ O $_3$  Schottky diodes with different Schottky metals. *J. Vacuum Sci. Technol. B* **35**, 03D113 (2017).

- M. Tadjer: Ohmic Contacts to Ga203. In *Gallium Oxide Technology*, *Devices and Applications*, edited by S. Pearton, M. Mastro and F. Ren (Elsevier, Oxford, 2018), pp. 413–434.

- 44. T. Oshima, R. Wakabayashi, M. Hattori, A. Hashiguchi, N. Kawano, K. Sasaki, T. Masui, A. Kuramata, S. Yamakoshi, and K. Yoshimatsu: Formation of indium—tin oxide ohmic contacts for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. *Japan J. Appl. Phys.* **55**, 1202B7 (2016).

- 45. D. Splith, S. Müller, F. Schmidt, H. Von Wenckstern, J.J. van Rensburg, W.E. Meyer, and M. Grundmann: Determination of the mean and the homogeneous barrier height of Cu Schottky contacts on heteroepitaxial β-Ga<sub>2</sub>O<sub>3</sub> thin films grown by pulsed laser deposition. *Physica status solidi* (a), 211, 40–47 (2014).

- 46. M. Higashiwaki, K. Konishi, K. Sasaki, K. Goto, K. Nomura, Q. Thieu, R. Togashi, H. Murakami, Y. Kumagai, B. Monemar, A. Koukitu, A. Kuramata, and S. Yamakoshi: Temperature-dependent capacitance–voltage and current–voltage characteristics of Pt/Ga<sub>2</sub>O<sub>3</sub> (001) Schottky barrier diodes fabricated on n-Ga<sub>2</sub>O<sub>3</sub> drift layers grown by halide vapor phase epitaxy. Appl. Phys. Lett., 108, 133503 (2016).

- 47. S. Ahn, F. Ren, L. Yuan, S.J. Pearton, and A. Kuramata: Temperature-dependent characteristics of Ni/Au and Pt/Au Schottky diodes on β-Ga<sub>2</sub>O<sub>3</sub>. ECS J. Solid State Sci. Technol. 6, P68–P72 (2017).

- 48. A. Armstrong, M.H. Crawford, A. Jayawardena, A. Ahyi, and S. Dhar: Role of self-trapped holes in the photoconductive gain of β-gallium oxide Schottky diodes. J. Appl. Phys., 119, 103102 (2016). https://doi.org/10.1063/1.4943261.

- S. Oh, G. Yang, and J. Kim: Electrical characteristics of vertical Ni/β-Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes at high temperatures. *ECS J. Solid State Sci. Technol.* 6, Q3022–Q3025 (2017).

- 50. E. Farzana, Z. Zhang, P. Paul, A.R. Arehart, and S.A. Ringel: Influence of metal choice on (010)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier properties. *Appl. Phys. Lett.* **110**, 202102 (2017). https://doi.org/10.1063/1.4983610.

- 51. W. Schottky: Deviations from Ohm's law in semiconductors. *Physik. Zeitschr* **41**, 570–573 (1940).

- 52. W. Mönch: Valence-band offsets of InGaZnO<sub>4</sub>,LaAIO<sub>3</sub> and SrTiO<sub>3</sub> heterostructures explained by interface-induced gap states. *J. Mater. Sci.: Mater. Electron.* 29, 19607–19613 (2018). https://doi.org/10.1007/s10854-018-0161-3.

- R.L. Anderson: Experiments on Ge-GaAs heterojunctions. Solid-State Electron. 5, 341–351 (1962).

- 54. N.F. Mott: Note on the contact between a metal and an insulator or semiconductor. *Proc. Cambridge Philos. Soc.* 34, 568–572 (1938).

- 55. C. Fares, F. Ren, E. Lambers, D.C. Hays, B.P. Gila, and S.J. Pearton: Band alignment of atomic layer deposited SiO<sub>2</sub> on (010) (Al<sub>0.14</sub>Ga<sub>0.86</sub>)<sub>2</sub>O<sub>3</sub>. J. Vac. Sci. Technol. B 36, 061207 (2018).

- 56. P.H. Carey, F. Ren, D.C. Hays, B.P. Gila, S.J. Pearton, S. Jang, and A. Kuramata: Conduction and valence band offsets of LaAl<sub>2</sub>O<sub>3</sub> with (-201) β-Ga<sub>2</sub>O<sub>3</sub>. J. Vac. Sci. Technol. B. 35, 041201 (2017), https://doi.org/10.1116/1.4984097.

- 57. P. Carey, F. Ren, D.C. Hays, B.P. Gila, S.J. Pearton, S. Jang, and A. Kuramata: Band alignment of atomic layer deposited SiO<sub>2</sub> and HfSiO<sub>4</sub> with (-201)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. *Jpn. J. Appl. Phys.* **56**, 071101 (2017). https://doi.org/10.7567/JJAP.56.071101.

- 58. P. Carey, F. Ren, D.C. Hays, B.P. Gila, S.J. Pearton, S. Jang, and A. Kuramata: Band alignment of Al<sub>2</sub>O<sub>3</sub> With (–201) β-Ga<sub>2</sub>O<sub>3</sub>. *Vacuum* **142**, 52 (2017), https://doi.org/10.1016/j.vacuum.2017.05.006.

- 59. D.C. Hays, B.P. Gila, S.J. Pearton, and F. Ren: Energy band offsets of dielectrics on InGaZnO<sub>4</sub>. Appl. Phys. Rev. 4, 021301 (2017), https:// doi.org/10.1063/1.4980153.

- 60. C. Fares, F. Ren, E. Lambers, D.C. Hayes, B.P. Gila, and S.J. Pearton: Band offsets for atomic layer deposited HfSiO<sub>4</sub> on (Al<sub>0.14</sub>Ga<sub>0.86</sub>)<sub>2</sub>O<sub>3</sub>. ECS J. Solid State Sci. Technol. 7, P519 (2018).

- 61. K. Ghosh and U. Singisetti: Calculation of electron impact ionization coefficient in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, 72nd Device Research Conference (2014), pp. 71–72.

- J.C. Yang, S. Ahn, F. Ren, S.J. Pearton, S. Jang, J. Kim, and A. Kuramata: High reverse breakdown voltage Schottky rectifiers without edge termination on Ga<sub>2</sub>O. *Appl. Phys. Lett.* 110, 192101 (2017).

- 63. J.C. Yang, F. Ren, M. Tadjer, S.J. Pearton, and A. Kuramata: 2300 V reverse breakdown voltage Ga<sub>2</sub>O<sub>3</sub> Schottky rectifiers. *ECS J. Solid State Sci. Technol.* 7, P92–P97 (2017).

- 64. J. Yang, S. Ahn, F. Ren, S.J. Pearton, and A. Kuramata: High breakdown voltage (-201)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky rectifiers. *IEEE Electron Dev. Lett.* **38**, 906–909 (2017).

- 65. L. Cao, W. Wang, G. Harden, H. Ye, R. Stillwell, A.J. Hoffman, and P. Fay: Experimental characterization of impact ionization coefficients for electrons and holes in GaN grown on bulk GaN substrates. *Appl. Phys. Lett.* 112, 262103 (2018).

- 66. K.G. McKay and K.B. McAfee: Electron multiplication in Si and Ge. *Phys. Rev.* **91**, 1079 (1953).

- 67. K.G. McKay: Avalanche breakdown in Si. Phys. Rev. 94, 877 (1954).

- A.G. Chynoweth and K.G. McKay: Threshold energy for electron-hole pair production by electrons in Si. *Phys. Rev.* 108, 29 (1957).

- 69. A.G. Chynoweth: Ionization rates for electrons and holes in Si. *Phys. Rev.* **109**. 1537 (1958).

- 70. A.G. Chynoweth and G.L. Pearson: Effect of dislocations on breakdown in Si p-n junctions. *J. Appl. Phys.* **29**, 1103 (1958).

- M. Grundmann, F. Klüpfel, R. Karsthof, P. Schlupp, F. Schein, D. Splith, C. Yang, S. Bitter, and H. von Wenckstern: Oxide bipolar electronics: materials, devices and circuits. *J. Phys. D: Appl. Phys.* 49, 213001 (2016).

- 72. S. Gao, Y. Wu, R. Kang, and H. Huang: Nanogrinding induced surface and deformation mechanism of single crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. *Mat. Sci. Semicon. Proc.* **79**, 165–170 (2018).

- 73. Y.Q. Wu, S. Gao, and H. Huang: The deformation pattern of single crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> under nanoindentation. *Materials Sci. Semicon. Proc.* **71**, 321–325 (2017).

- 74. T. Oshima, A. Hashiguchi, T. Moribayashi, K. Koshi, K. Sasaki, A. Kuramata, O. Ueda, T. Oishi, and M. Kasu: Electrical properties of Schottky barrier diodes fabricated on (001) β-Ga<sub>2</sub>O<sub>3</sub> substrates with crystal defects. *Jpn. J. Appl. Phys.* **56**, 086501 (2017).

- K. Nakai, T. Nagai, K. Noami, and T. Futagi: Characterization of defects in β-Ga<sub>2</sub>O single crystals. *Jpn. J. Appl. Phys.* 54, 015201 (2015).

- 76. M. Kasu, T. Oshima, K. Hanada, T. Moribayashi, A. Hashiguchi, T. Oishi, K. Koshi, K. Sasaki, A. Kuramata, and O. Ueda: Crystal defects observed by the etch-pit method and their effects on Schottky-barrier-diode characteristics on β-Ga<sub>2</sub>O<sub>3</sub>. *Jpn. J. Appl. Phys.* **56**, 091101 (2017) https://doi.org/10.7567/JJAP.56.091101.

- J.B. Varley, H. Peelaers, A. Janotti, and C.G. Van de Walle: Hydrogenated cation vacancies in semiconducting oxides. *J. Phys.: Condens. Matter* 23, 334212 (2011).

- 78. S. Lany: Defect phase diagram for doping of  $Ga_2O_3$ . APL Mater. **6**, 046103 (2018).

- 79. S. Ohira, and N. Arai: Wet chemical etching behavior of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystal. *Phys. Status Solidi. C* **9**, 3116–3118 (2008).

- 80. Z. Hu, K. Nomoto, W. Li, Z. Zhang, N. Tanen, Q.T. Thieu, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H.G. Xing: Breakdown mechanism in 1 kA/cm² and 960 V E-mode β-Ga<sub>2</sub>O<sub>3</sub> vertical transistors. *Appl. Phys. Lett.* **113**, 122103 (2018).

- M.J. Tadjer: Cheap ultra-wide bandgap power electronics? gallium oxide may hold the answer. ECS Interface 27, 49–52 (2018). https://doi.org/10. 1149/2.F05184if.